感谢IT之家网友 华南吴彦祖 的线索投递!

IT之家 6 月 28 日消息,铠侠(Kioxia)结束为期 20 个月的 NAND 闪存减产计划,日本两座工厂生产线开工率提升至 100% 之后,上周披露了其 3D NAND 路线图计划。

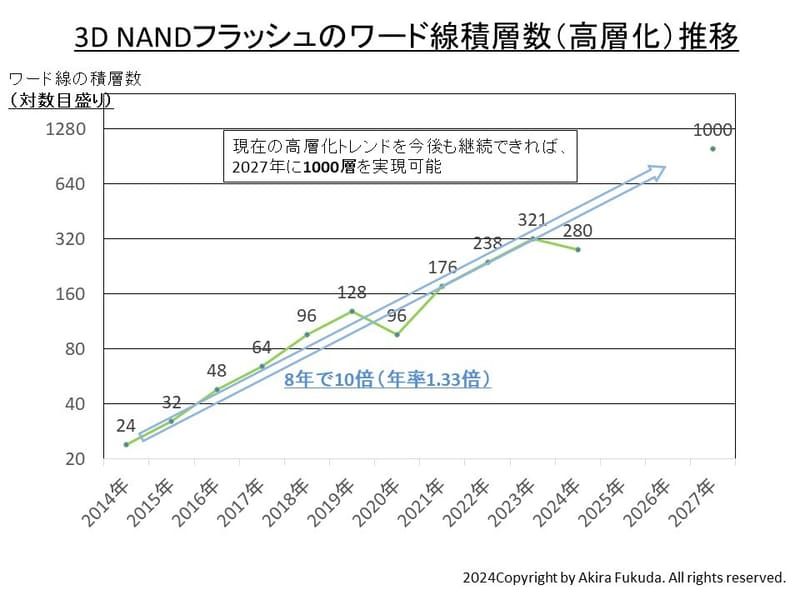

根据 PC Watch 和 Blocks & Files 的报道,铠侠目标在 2027 年达到 1000 层的水平。

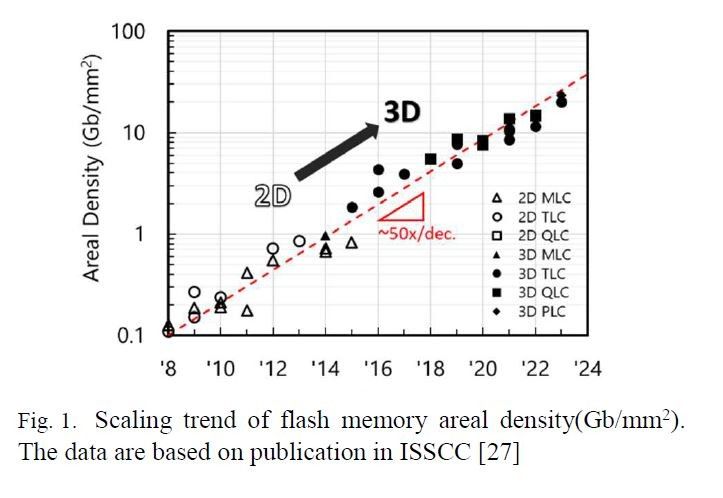

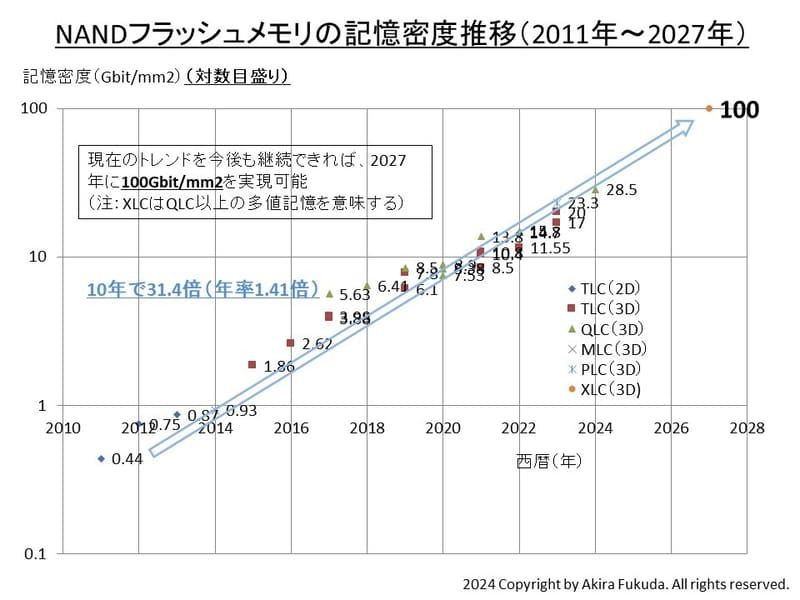

IT之家援引媒体报道,3D NAND 在 2014 年只有 24 层,到 2022 年达到 238 层,8 年间增长了 10 倍。而铠侠目标以平均每年 1.33 倍的速度增长,到 2027 年实现 1000 层堆叠。

三星在上个月表示,计划 2030 年之前推出超过 1000 层的先进 NAND 闪存芯片,其中铪基薄膜铁电(Hafnia Ferroelectrics)将成为这项成就的关键。

在摘要部分中写到,在金属带工程栅极中间层(BE-G.IL)、铁电(FE)开关、沟道中间层(Ch.IL)和硅(MIFIS) FeFET 架构中,使用 FE 开关相互作用,来显著提高性能,表明 hafnia FE 成为扩展 3D VNAND 技术发展的关键推动力。

在 3D NAND 闪存的层数挑战上,铠侠似乎比三星更有野心。

首先是政策和资本扶持,铠侠受益于内存行业的复苏,最近获得了日本政府的补贴和银行财团的额外融资,此外该公司还计划今年年底 IPO 上市,让铠侠有充足的资金,追求技术进步和成本优化。

其二是技术演进和积累,铠侠预测到 2027 年 NAND 芯片密度将达到 100 Gbit / mm2,实现 1000 层。

提高 3D NAND 芯片的密度不仅仅是在芯片上堆叠更多层,因为每层的边缘都需要暴露以进行字线电气连接。这为芯片提供了阶梯状轮廓,随着层数的增加,阶梯所需的芯片面积也会增加。

铠侠雄心勃勃地计划到 2027 年实现 1000 层技术,这是迄今为止所有制造商宣布的最高层数。然而,要达到这一里程碑,就必须从 TLC(每单元 3 位)过渡到 QLC(每单元 4 位),甚至可能过渡到 PLC(每单元 5 位)。其中涉及的技术挑战是巨大的,铠侠能否在 2027 年之前实现这一市场里程碑还有待观察。

还没有评论,来说两句吧...